我们都知道通信从大的方面有两种:串行和并行。串行的最大优点是占用总线少,但是传输速率低;并行恰恰相反,占用总线多,传输速率高。市面上有很多这样的芯片,有串入并出的(通俗讲就是 一个一个进,最后一块出来),有并入串出的(相对前者而言)。具体用哪种类型要根据我们得实际情况。比如利用单片机显示数码管单纯的显示一个数码管如果仅仅是为了显示 那么动用单片机一个端口(如P0或P1/P2/P3)那没有什么,当然这里我说的数码管是8段的(如果利用BCD类型 16进制数码管那么只需四个即可)就拿51类型的单片机来说,总共32个I/O口,一般如果不是做太大的工程是完全够用的,但有些时候你会恨单片机怎么不多长几条“腿”,怎么省还是不够用。这个时候就需要用到并转串或者串转并芯片来进行IO口的扩展,74HC165就是一种并行转串行的芯片。

74HC165是一款高速CMOS器件,74HC165遵循JEDEC标准no.7A。74HC165引脚兼容低功耗肖特基TTL(LSTTL)系列。 74HC165芯片有8位移位寄存器(并行输入,互补串行输出) 74hc165特性:8位同步并行输入、异步串行输出、兼容JEDEC标准no.7A、ESD保护

简要说明

54/74165为8位移位寄存器,其主要电特性的典型值如下:

74hc165基本参数

电压:2.0~6.0V

驱动电流:+/-5.2mA

传输延迟:16ns@5V

最高频率:56MHz@5V

逻辑电平:CMOS

工作温度:-40~+85℃

封装:SO16,SSOP16,DIP16,TSSOP16

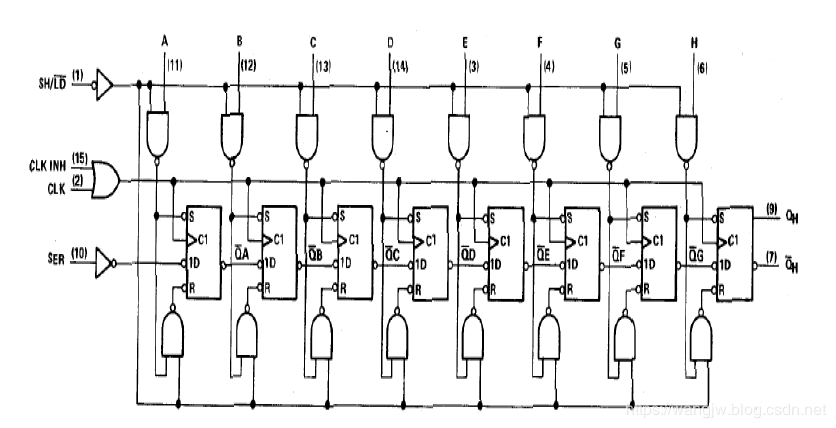

逻辑电路图:

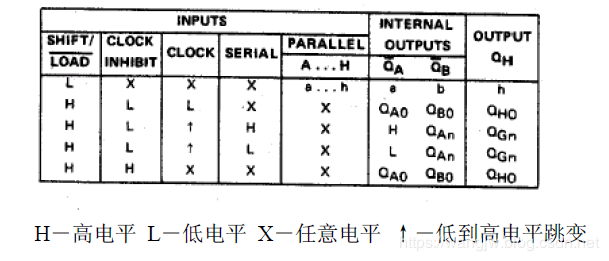

真值表:

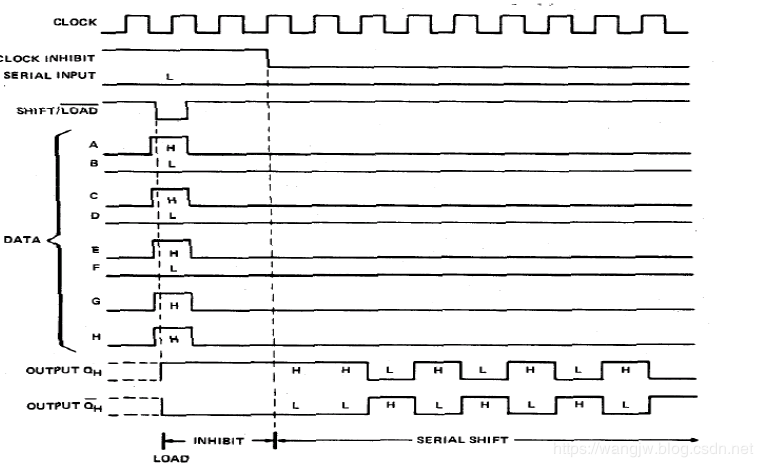

时序图:

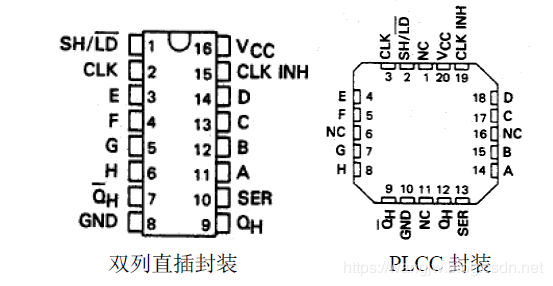

74HC165芯片的芯片引脚图:

引脚功能介绍

1、CLK,CLK INH : 时钟输入端(上升沿有效)

2、A-H :并行数据输入端

3、SER :串行数据输入端,为串行输入端 、 将数据串行进入到寄存器中、在每一个时钟的上升沿向右移动一位,利用这种特性,只要把 QH输出连接到下一级的SER输入 既可实现并转串扩展

4、QH : 输出端

5、!QH :互补输出端

6、SH/!LD:移位控制/置入控制(低电平有效), 为低电平时 并行数据进入移位寄存器中,为高电平时并行数据不能传进移位寄存器

①当输入端(SH/LD)为低:

从D0到D7口输入的并行数据将被异步地读取进寄存器内,然后通过DS输出。

②当输入端(SH/LD)为高:

数据将从DS(10引脚)输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位。利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。(在我们的开发板,DS端是悬空的),通过时钟管脚,上升沿有效,在每个时钟脉冲的上升沿向右移动一位(D0→D1→D2→D3→…→D7)一位一位将数据往外读出和移出。

芯片工作方法:

其实看一个芯片是如何使用的,不只是看引脚功能,更重要的是要看时序图和真值表,从其中我们可以详细的了解到它是如何使用的,然后转化成程序代码即可。

从上面我们的真值表和时序图中我们要特别注意几个端口的变化,真值表中SH/LD只有在高电平的时候方才有效;CLK,CLK INH只有当其中一个为低电平的时候,另一个时钟才能正确的输入,这是非常重要的(一般的我们在使用时,可以将其中的一个直接接地,另一个做时钟输入端口使用)。但是我们做事要细心,要一丝不苟,从时序图中我们看到SH/LD有一个负脉冲这是什么缘故呢?在程序设计中如果忽略了此处,那么注定结果是悲剧的。从SH/LD的全称是: SHIFT/LOAD 这说明它有两种功能( SHIFT英文意思是移位,LOAD是装载) ,故美其名曰: 移位控制(高电平有效)/置入控制端口(低电平有效)。在单片机接收数据前,必须将该引脚拉低,目的是为了将并行数据A--H上得数据装载到内部寄存器中,这里体现的时LOAD功能;接下来在接收数据的过程中必须将该引脚拉高,目的是为了使寄存器中的数据可以移动,从而从QH或QN'中移入单片机。这里体现的是SHIFT功能。74hc165中最重要的一个引脚就是该引脚 至于说时钟电路就显得逊色多了。我们只需将单品机的某一个端口拉低或抬高即可,这样数据就一步一步的被接收了。请务必记得上升沿有效。

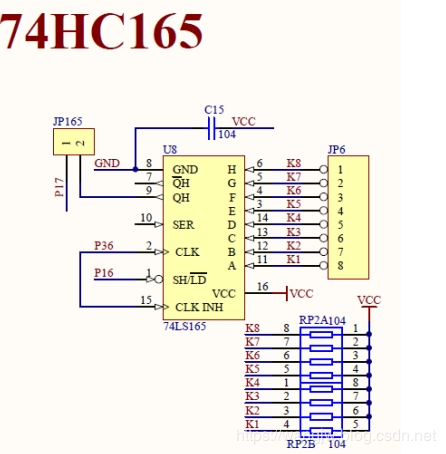

接下来看下使用到的开发板相关模块的电路原理图:

开发板上的165并行输入端口 连接的IO口是与8个独立键盘相互共用,可以做独立键盘的输入扩展、QH串行输出端口是连接了P17引脚 加了个短路冒不用的时候可以断开避免影响P17的电平。 每次按键按下时,相应的发光二极管就会被点亮。

硬件连线图:

24H咨询平台

24H咨询平台 微信公众号

微信公众号